# 受動素子内蔵ウエハレベルパッケージ

## On-Chip Passive Devices Embedded in Wafer-Level Package

K. Masu, K. Okada, K. Itoi, M. Sato, H. Abe & T. Ito

次世代パッケージ技術の一つとして期待されるウエハレベルパッケージに、厚膜銅めっきならびに厚膜 樹脂形成技術を応用したインダクタを形成し、高周波特性の評価を行った。作製したスパイラルインダク タ、ソレノイドインダクタは高い Q値と自己共振周波数を示すとともに、その値は、シミュレーション値 ともよい一致を示した。受動素子内蔵型のウエハレベルパッケージが、RF回路の特性を向上させることが 可能であることを確認した。

On-chip high-Q inductors on Si substrate embedded in wafer-level package have been fabricated. These inductors consisted of a thick Cu electroplated rerouting to reduce electrical resistance and a thick resin layer to separate the inductors typically 20  $\mu$ m from Si substrate. The fabricated spiral and solenoid-type inductors showed high-Q and high-SRF compared to on-chip inductor fabricated standard CMOS process. In addition, the measured results of Q, L and SRF corresponded well with the simulated values by electromagnetic simulators, HFSS and Sonnet. This technology realizes high performance RF-IC with the embedded inductors in wafer-level packages.

#### 1. まえがき

現在爆発的に普及している携帯電話や、無線LAN、RF-IDといったワイヤレス機器の進展に伴い、それらの機器で使用されるRF-ICもまた、さらなる高性能化、小面積化、低コスト化が求められている。プロセス微細化の進展、ウエハ口径の大口径化、製造プロセスにおけるノウハウ蓄積という面を反映し、近年、Si CMOSプロセスを用いたGHz帯でのRFアナログ回路の利用が増大し、研究開発も精力的に進められている。

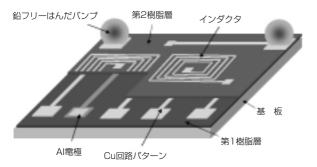

図1 WLP内蔵スパイラルインダクタの模式図 Schematic illustration of on-chip inductors in WLP

RFアナログ回路では、能動素子に加えて、抵抗 (R)、インダクタ (L)、コンデンサ (C) といった受動素子を集積する必要がある.しかしながら、これまでGHz帯デバイス用基板として使用されてきた半絶縁性基板のGaAsに対し、Si上に形成される受動素子の中で、最も性能が制限されるのはインダクタであり、その要因は二つある.一つは、インダクタとSi基板との結合により損失が生じる点である. RFアナログ回路で用いられるインダクタは、CMOSプロセスによってSi基板上にオンチップインダクタとして形成されるため、インダクタから発生した磁束がSi基板内を通過し、誘導損失を誘起する.加えて、インダクタ直下に能動素子を配置することができず、チップ面積の増大という問題も引き起こす.

第二の問題としてインダクタの直流抵抗成分の増大があげられる。多層配線プロセスにおける AIの配線抵抗が原因となり,結果としてインダクタの性能を表す指標である品質係数 (Q) の値は3~7程度が限界である。実際,Low Noise Amp (LNA) における位相雑音の約30%が,Si基板上のオンチップインダクタに起因するという報告 P(X)0 や,インダクタの P(X)0 を30から40%程度改善することにより,P(X)1 Voltage Controlled Oscillator (VCO) の消費電力を半分以下にすることが可能であるという報告 P(X)2 もあり,まずは,P(X)6 を超えるインダクタが求められている。

これらの問題を解決するために、インダクタパターンの 最適化やシールドパターンの利用といったCMOSプロセス

<sup>\*1</sup> マイクロデバイス開発部

<sup>\*2</sup> マイクロデバイス開発部長

上での試みや $3^{3}$ ~ $5^{5}$ ,インダクタ直下のSi基板をエッチングによって除去,犠牲層エッチングを用いたエアコアタイプの三次元インダクタといったMEMS技術を用いたインダクタも報告されている $6^{3}$ ~ $9^{5}$ . しかし,これらのインダクタでは性能向上が不十分であったり,パッケージングを含めた長期信頼性の不安といった問題を抱えている.

これに対し、我々はすでにファウンダリサービスとして 量産を行っているウェハレベルパッケージ(WLP)技術 の中で、厚膜樹脂層・銅配線形成技術といった特徴的な要素技術を応用し、これらの課題を克服した高性能インダク タを開発した。図1にWLP内蔵スパイラルインダクタの模 式図を示す。本インダクタはWLPの構造・プロセスを利 用して、IC上の絶縁樹脂層と封止樹脂層の間に、WLP工程と同一工程によって形成される。高Q値を持つインダクタやRF-ID用アンテナといった受動素子をWLPに内蔵することで、通常のCMOSプロセスでは作製不可能な高性能受動素子の作製と、WLPによる高密度パッケージング加工の両方を同時に行うことが可能となり、性能面、実装面での強力なアドバンテージになると考えられる。CMOSプロセスで形成された従来型のオンチップインダクタと比較したWLP内蔵インダクタの利点は、以下の通りである。

1. 絶縁樹脂によってインダクタがシリコン基板と分離されるため, Si基板内に誘起される渦電流損失を低減す

表1 作製したインダクタの設計値 Geometrical patterns and typical dimensions of the fabricated inductors

| 項 目      | スパイラル                                           | ソレノイド |

|----------|-------------------------------------------------|-------|

| 巻き数      | 2.5~5.5                                         | 5     |

| Si基板の比抵抗 | 4 (A-type), >1k (B-type) Ωcm                    |       |

| Cu膜厚     | 5 (1 <sup>st</sup> ), 10 (2 <sup>nd</sup> ) μm  |       |

| 樹脂膜厚     | 10 (1 <sup>st</sup> ), 10 (2 <sup>nd</sup> ) μm |       |

| ライン/スペース | 30/20 μ m                                       |       |

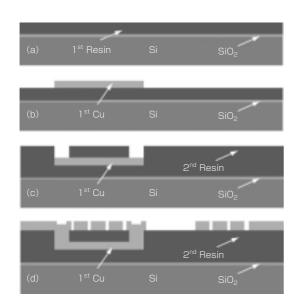

図2 WLP内蔵スパイラルインダクタのプロセスフロー Schematic cross-sectional process diagram of the embedded inductor

- ることが可能である。特にスパイラル形状のインダク タのように、Si基板と垂直方向に磁界が発生するデバ イスにおいて効果が大きい。

- 2. 電解めっきによって厚膜の銅層を形成するため、配線 抵抗の低抵抗化が可能である.

- 3. 基板との実装はバンプによって行われるため、ワイヤボンドに起因する浮遊インダクタンスの低減が可能である。

- 4. 現有のWLP製造工程と同一のプロセスによって作製可能であるため、付加コストが少なく、かつ、高い実装信頼性<sup>10)</sup>、量産性を確保している.

また、当社のWLP工程は、多層樹脂層や多層配線層を 形成することが容易であることを特徴としているため、他 のWLPプロセスと比較して、特に基板損失低減の効果が 高いプロセスを構築することが可能である.

## 2. 構造と作製プロセス

本論文では、ベアSiウエハに作製したスパイラル型<sup>111</sup>、ソレノイド型インダクタの高周波特性を報告する。ソレノイド型インダクタでは、インダクタから発生した磁界がSi基板を横切らない構造となるため、基板の影響がさらに軽減されるとともに、チップ下部が導電面となるような用途の場合、特に有効であると考えられる。

表1に作製したインダクタの設計値、図2にスパイラルインダクタのプロセスフローを示す。インダクタの設計は電磁界シミュレータHFSS, Sonnetを用いた。

## 3. 結果と考察

#### 3.1 電気特性

作製したインダクタのSEM写真を図3に示す。インダクタの評価項目として,DC抵抗測定と高周波特性(Q, L) の測定を行った。当社の電解銅めっき層の電気抵抗は純銅のそれとほぼ同一であり,作製したインダクタのDC抵抗は,設計値とほぼ一致した。例えば,3.5巻きスパイラルインダクタのDC抵抗値は約 $0.3\,\Omega$ であるが,この値は同一の平面構造を持った膜厚 $1.5\,\mu$  mの Al 配線インダクタの約10分の1であり,WLP構造を応用することで,配線抵抗の大幅な低抵抗化が可能となった。

図3 作製したインダクタのSEM写真 (左) スパイラルインダクタ, (右) ソレノイドインダクタ SEM photograph of a fabricated inductor (Left) spiral inductor, (Right) solenoid inductor

#### 3.2 高周波特性

高周波特性は、ネットワークアナライザならびに高周波 プローバを用いてインダクタのSパラメータを測定し、以 下の式を用いてQ, Lを求めた $^{12}$ .

$$Q = \frac{-\operatorname{Im} \{Y_{11}\}}{\operatorname{Re} \{Y_{11}\}} \qquad ---- (1)$$

$$L = \frac{1}{2\pi f} \text{Im} \left\{ \frac{1}{Y_{11}} \right\} - - - - (2)$$

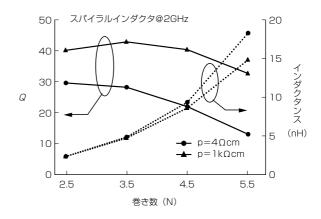

周波数2GHzにおけるスパイラルインダクタの巻数とQ, Lの関係を図4L, またオンチップインダクタの特性値を議論する際に重要な等価回路モデルを図5Lに示す。3.5巻きのスパイラルインダクタでは、基板抵抗 $4\Omega$  cm,  $1k\Omega$  cmにおいてそれぞれ、Q=29.4, 42.9を得た。この値は従来のA1配線によるインダクタのQ(3L7)と比較すると十分に高く、L8 以上P技術により、高性能なオンチップインダクタを作製可能であることを確認した。また、高比抵抗基板のインダクタのL9 値はL9 を超え、低比抵抗基板のそれを大きく上回っていることがわかる。このことは、絶縁樹脂層によってインダクタとL9 に基板が約L9 L1 m分離されているにもかかわらず、インダクタから発生した磁束がL1 を 板内を通過し、渦電流損失が生じていることを意味する。

図4より、3.5巻きのスパイラルインダクタにおいて、L=5.0、4.9nHを得た(f=2GHz). このインダクタにおけるインダクタンス値の設計値は5.0nHであり、電磁界シミュレータによるインダクタの設計は、WLP技術を用いたインダクタについても有効であると言える。また、電磁界シミュレータによる解析値と実測値は、Qが約10%, L値では約2%以内の誤差範囲であり、精度の高い設計が可能であることが明らかとなった。

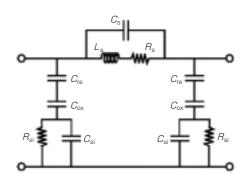

また、インダクタのデザインキット作製時に重要なデバイスパラメータを、ADS(Advanced Design Simulator)によって求めた。等価回路モデルは図5に示すモデルである。その結果、低比抵抗基板の3.5巻きスパイラルインダクタにおいて、 $R_{Si}$ の値が約5,000  $\Omega$ となることを確認した。6層 Al 配線を用いた CMOS プロセスによるオンチップインダクタのそれが数100  $\Omega$ であることから、厚膜樹脂層によるインダクタとSi基板との分離効果が大きいことがわかる。

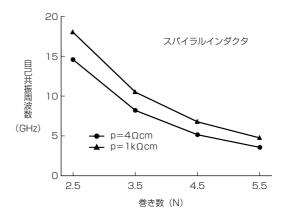

図6にスパイラルインダクタの巻き数と自己共振周波数の関係を示す。3.5巻きのスパイラルインダクタにおいて,自己共振周波数は約9GHzに達した。一般的に,自己共振周波数は動作周波数の3倍程度必要であることから,このインダクタは,想定する2GHz帯での動作に適していると考えられる。さらにソレノイドインダクタでは,自己共振周波数が20GHzを超えることを確認した(L=2nH)。これは,スパイラルインダクタと比較して,Si基板を通過する磁束の影響が少ないためと考えられる。

## 3.3 スパイラル・ソレノイドインダクタの比較

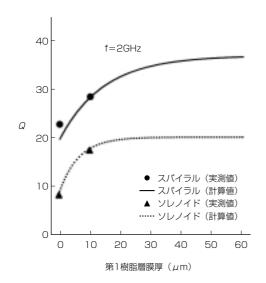

図7に第1樹脂層の膜厚をパラメータとしたときの,スパイラルインダクタとソレノイドインダクタとのQ値の比較を示す.スパイラルインダクタでは,膜厚の増加に伴っ

図4 作製したスパイラルインダクタの QとLの関係 (f = 2GHz) The measured results of Q and L at f = 2GHz of fabricated inductors as a function of different number of turns

図 5 インダクタの等価回路モデル The equivalent circuit of the embedded inductor

図 6 作製したスパイラルインダクタの自己共振周波数 (SRF) The measured results of  $f_{\rm res}$  at  $f=2{\rm GHz}$  of fabricated inductors as a function of different number of turns

てQ値が増加するのに対し、ソレノイドインダクタでは、 樹脂層の膜厚約 $20~\mu$  mからQ値の値がほぼ一定となるこ とがわかる。このことからソレノイドインダクタでは、第 1樹脂層の膜厚を変化させることにより、Si基板の影響を ほぼ回避できる構造が可能であることが明らかとなった。

図 7 スパイラルインダクタとソレノイドインダクタのQ値の比較 Comparison of *Q* between spiral and solenoid-type as a function of the thickness of the first resin layer

## 4. む す び

WLP技術を応用しWLP内蔵インダクタを開発した.作製したインダクタの特性値は、CMOSプロセスで作られたインダクタの特性値を上回り、また解析値とも良く一致した.今後は、アンテナやRF-IDといった様々なワイヤレス機器への応用を目指したインダクタの開発を行うとともに、動作周波数帯でのインダクタンス値とQ値に応じてインダクタのレイアウトが決定されるようなデザインキット

の整備を行う予定である.

## 参考文献

- 1) K.S. Yeo: Proc. of Microwave Workshop, pp.1-4, 2004

- 2) 益, 岡田:応用物理, Vol.73, No.12, pp.1172-1178, 2004

- 3) J. R. Long: IEICE Trans. Electron., Vol.E86-C, No.6, pp.1022-1030, 2003

- 4) Y. Sugimoto, et al.: Journal of Jpn. Institute of Electronics Packaging, Vol.6, No.6, pp.473-480, 2003

- 5) S. Lee, et al.: IEICE Trans. Electron., Vol.E84-C, No.6, pp.845-848, 2001

- 6) B. Piemas, et al.: IEEE Trans. Microwave Theory Tech., Vol.50, No.8, pp.1942-1948, 2003

- 7) J. Y. Park, et al.: IEEE Trans. Magn., Vol.35, No.5, pp.3544-3546, 1999

- 8) E. C. Park, et al.: IEEE Trans. Microwave Theory Tech., Vol.51, No.1, pp.289-296, 2003

- 9) J.B. Yoon, et al.: IEEE Trans. Microwave Theory Tech., Vol.51, No.1, pp.279-288, 2003

- N. Sadakata, et al.: SEMI Technology Symposium 2000., pp.123-127, 2000

- 11) K. Itoi, et al.: Proc. of IEEE MTT-S Int. Microwave Symp. Dig., 2004 (to be published)

- 12) S. A. Wartenberg,: RF Measurements of Die and Packages, Boston: Artech House, 2002